FOB Price

Obtenir le dernier prix( Negotiable )

|Minimum Order

Localit�:

-

Prix de commande minimale:

-

Commande minimale:

10 Piece

Packaging Detail:

box

Delivery Time:

15days

Supplying Ability:

-

Payment Type:

T/T

China

Personne à contacter Mr. He

17-8 Wensu, Shenyang, Liaoning

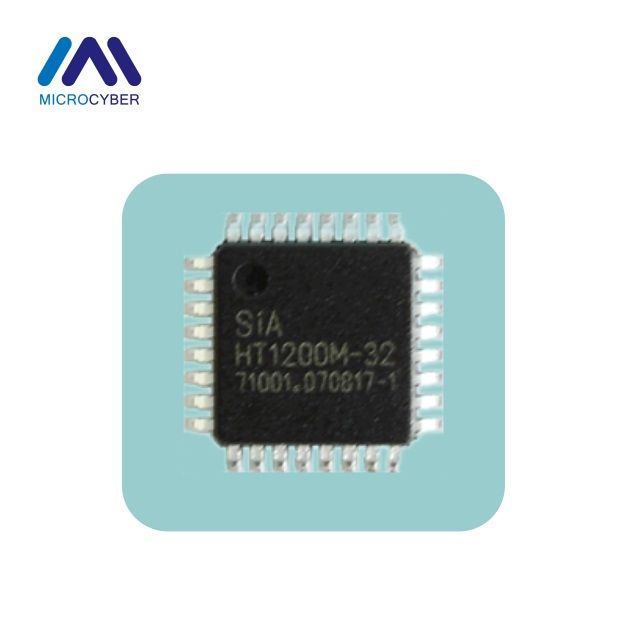

General Description

FBC***9 is a fieldbus interface and controller IC which conforms to IEC ****8 filedbus physical layer definition. It supports typical embedded CPU and MCU, and satisfies the demands of high performance fieldbus masters or slavers.

FBC***9 contains Manchester data encoder and decoder on chip. It requires a medium interface and external filter for connection to a fieldbus system, and can automatically correct bus polarity. FBC***9 also contains 4k bytes embedded data RAM, applying DMA controller. The implementation of message transmission and address resolution can be executed without CPU intervention. The Rx and Tx data status is available in status registers of FBC***9, such as status of line operation, code error, frame loss, frame collision.

FBC***9 implement a portion of data-link layer function. Tx/Rx frame check sequence (FCS), *6 bits 1ms timer, *6 bits 1/*2ms timer, *6 bits octet time timer, frame code decoding and address resolution.

Features

FBC***9 is designed for fieldbus physical and part data link communication functions, details list below: